“摩尔定律”[1]成功预测了半导体领域的技术发展,然而随着传统的硅晶体管的尺寸接近理论极限——栅极长度5纳米(低于此极限将产生“短沟道效应”,晶体管就会失效),集成电路上元器件数目的增加速度开始放缓。要知道晶体管的最小尺寸越小,单位面积的芯片(比如电脑和智能手机上的CPU)就能包括更多晶体管,芯片性能就越强而价格就越便宜。为了打破这一桎梏,科学家们开始寻找新的材料,试图代替接近理论极限的“硅”。

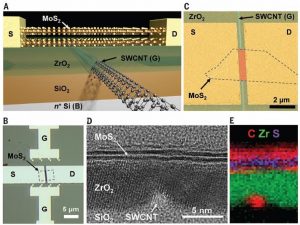

近日,加州大学伯克利分校(UC Berkeley)的Ali Javey教授课题组在Science发表文章,制备出栅极长度仅有“1纳米”的晶体管,这种晶体管采用二硫化钼(MoS2)材料,使用单壁碳纳米管作栅极电极。(MoS2 transistors with 1-nanometer gate lengths. Science, 2016, 354, 99-102, DOI: 10.1126/science.aah4698)

传统硅(Si)晶体管被认为栅极长度不能低于临界尺寸5nm,否则会出现严重的短沟道效应,导致源极-漏极间的量子隧穿效应,电子就能够“穿过”它面前的“障碍物”从而使得栅极失去静电调控能力。因此小于临界尺寸的晶体管无法处于关闭状态,不能形成有效的门电路。

想要制备出更小的晶体管,就需要寻找层状的半导体替代材料,并使其具有更低的介电常数、较大的带隙和较重的有效载流子质量。研究者选中了单壁碳纳米管做栅极电极,源极和漏极之间使用单层MoS2。通过研究过渡金属硫化物的能带结构,单层或几层MoS2已被证明优于Si材料并且不受其在晶体管中5nm的最低条件限制,其隧穿漏电流比Si小两个数量级以上。

通过实验,器件具有优异的开关特性,开关电流比约为106,并且其亚阈值摇摆幅度只有65 mV/dec。仿真结果显示该晶体管的有效沟道长度在关闭状态时约为3.9纳米,打开状态时约为1纳米。

当然,这一研究依然是处于实验室阶段,尚未实现批量生产并转移至实际芯片上。不过,研究者的工作让突破传统硅晶体管物理极限变的可能,通过新材料的应用,晶体管不会停步在5纳米,